### UNIVERSITY OF TWENTE.

September 5, 2022

### SYSTEM-ON-CHIP DESIGN **GETTING STARTED WITH VHDL**

SYSTEM-ON-CHIP DESIGN UT. **GETTING STARTED WITH VHDL**

September 2, 2022

### OUTLINE

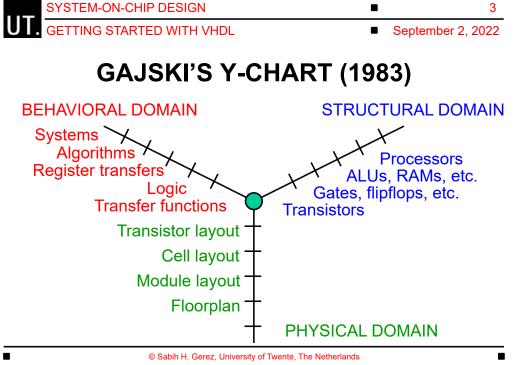

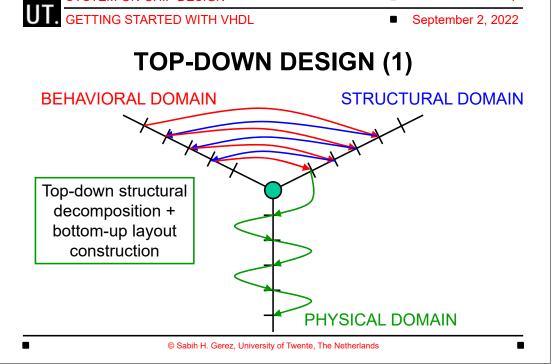

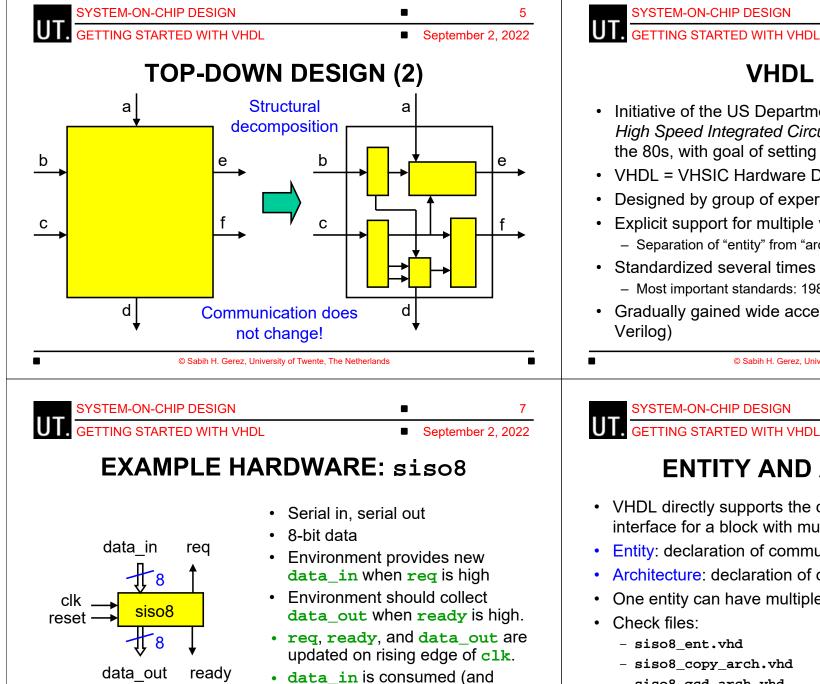

- Top-down design

- VHDL history •

- Main elements of VHDL

- Entities and architectures

- Signals and processes

- Data types

- Configurations

- Simulator basics

- The testbench concept

SYSTEM-ON-CHIP DESIGN

© Sabih H. Gerez, University of Twente, The Netherlands

should be stable) on rising edge

of clk.

© Sabih H. Gerez, University of Twente, The Netherlands

### **VHDL HISTORY**

- Initiative of the US Department of Defense, part of the Very High Speed Integrated Circuit (VHSIC) programme running in the 80s, with goal of setting a standard.

- VHDL = VHSIC Hardware Description Language

- Designed by group of experts

- Explicit support for multiple views:

- Separation of "entity" from "architecture"

- · Standardized several times by IEEE:

- Most important standards: 1987, 1993, 2008 (used here!), 2019.

- Gradually gained wide acceptance (together with rival language)

```

SYSTEM-ON-CHIP DESIGN

```

**GETTING STARTED WITH VHDL**

September 2, 2022

### ENTITY AND ARCHITECTURE

- VHDL directly supports the concept of one communication interface for a block with multiple descriptions of its contents.

- Entity: declaration of communication

- Architecture: declaration of content: behavior, structure or mix

- One entity can have multiple architectures.

- siso8 copy arch.vhd

- siso8 gcd arch.vhd

© Sabih H. Gerez, University of Twente, The Netherlands

September 2, 2022

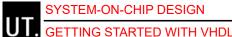

### DESCRIBING REGISTERS

• All registers: *positive edge-triggered flipflops* (copying data from input to output on rising clock edge) with asynchronous reset.

GETTING STARTED WITH VHDL

SYSTEM-ON-CHIP DESIGN

September 2, 2022

11

### COMBINATIONAL AND SEQUENTIAL LOGIC

- Points of attention: ٠

- Processes can model logic with or without internal memory, sequential resp. combinational logic.

- Sensitivity list

- Coding style for synchronous sequential logic with asynchronous reset.

September 2, 2022

10

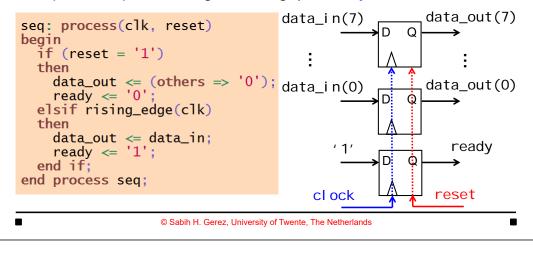

## LIBRARIES, PACKAGES, SIGNALS AND PROCESSES

- Points of attention:

- Library: precompiled design information, grouped by a *library name*.

- Package: design information of general nature to be used in more specific designs. Example: a collection of data types and functions that operate on them.

- Signal: a carrier of values that change in time, normally associated to a wire or wire bundle in hardware.

- Process: a description of how signals change their values. Multiple processes model parallelism.

© Sabih H. Gerez, University of Twente, The Netherlands

SYSTEM-ON-CHIP DESIGN

**GETTING STARTED WITH VHDL**

September 2, 2022

12

# SIMULATOR BASICS

- The simulation engine of VHDL is a so-called event-driven simulator.

- Events are signal changes. An event triggers new events after some delay.

- Events take place at some time. The simulator handles events in the order of their activation time.

- In VHDL processes are activated for events on signals in their sensitivity lists. Process activation generally creates new events.

- Even when no delay is specified in the VHDL code, the simulator will introduce an infinitesimal delay, a so-called delta delay.

SYSTEM-ON-CHIP DESIGN

### SIGNALS AND VARIABLES (1)

- A signal in VHDL is the equivalent of a physical wire.

- Processes communicate via signal changes.

- Signals are always declared outside a process.

- Signal assignments are indicated by <= and are never immediate, take at least a delta delay.

- Signal assignments can occur outside processes: concurrent assignment, a process on its own.

#### UT **GETTING STARTED WITH VHDL**

September 2, 2022

14

### SIGNALS AND VARIABLES (2)

A signal assignment corresponds to hardware: the combination of signals at the right-hand side produces the signal at the lefthand side.

Multiple assignments to the same signals is like shorting two outputs: it is not allowed unless the signal is "resolved".

© Sabih H. Gerez, University of Twente, The Netherlands

SYSTEM-ON-CHIP DESIGN

**GETTING STARTED WITH VHDL**

September 2, 2022

16

## DATA TYPES IN VHDL

- Few built-in data types: integers, characters, strings, time.

- Mechanism to define new data types by enumeration, arrays, records.

- Very common non-native data type: **std\_logic**, defined in standardized package std\_logic\_1164, compiled in library ieee (including functions such as Boolean operators).

- Actually an enumeration of 9 characters: '0', '1', 'z', 'U', 'x', '-', etc.

- Associated vector type std logic vector, with constants written as strings, e.g. "00101".

- std\_logic is a resolved type, i.e. a resolution function computes a signal value in the case of multiple drivers.

SYSTEM-ON-CHIP DESIGN 15 **UT**. GETTING STARTED WITH VHDL September 2, 2022 SIGNALS AND VARIABLES (3) Processes can also have local variables: ٠ - Declared inside a process - Not visible to other processes • Variable assignment is indicated by **:=** and is immediate.

© Sabih H. Gerez, University of Twente, The Netherlands

- It is therefore allowed to perform multiple assignments to a variable without advancing simulation time:

- This does not have a direct hardware equivalent.

- Avoid the use of variables in the hardware that you design!

13

September 2, 2022

**GETTING STARTED WITH VHDL**

17

### NUMERIC DATA TYPES

- A sequence of bits can be interpreted as a number.

- Multiple interpretations exist.

- The package numeric std, standardized by the IEEE, available in library ieee defines two interpretations for std logic vectors:

- signed: signed number encoded as 2's complement

- unsigned: positive binary numbers.

- VHDL has strong typing: assignments from std logic vector to signed/unsigned require type casting.

© Sabih H. Gerez, University of Twente, The Netherlands

**TESTBENCH** (2)

**GETTING STARTED WITH VHDL**

September 2, 2022

18

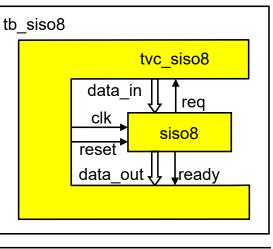

# **TESTBENCH (1)**

- Simulation is the most common method to verify the correctness of a design, the design under verification (DUV).

- In order to simulate a design, specific signal patterns need to be supplied to the inputs.

- It is convenient to use a universal HDL to describe this signal generation, in this case VHDL.

- It is also convenient to monitor the outputs of the DUV; sometimes input signals can be generated depending on the received outputs.

- This results in a test-vector controller (TVC) with opposite I/O patterns to the DUV.

# CONFIGURATIONS

- A VHDL simulator is supposed to store compiled versions of all architectures of an entity simultaneously.

- Question: how does one indicate which of the architectures should be simulated?

- Answer: VHDL configurations define which architectures to use for each entity all the way down the hierarchy.

- · Check files:

- conf tb siso8 copy.vhd

- conf\_tb\_siso8\_gcd.vhd

DUV + TVC = testbench (TB)

SYSTEM-ON-CHIP DESIGN

UT. GETTING STARTED WITH VHDL

- The testbench does not have any I/O signals!

- Check files:

- tb siso8.vhd

- Note: TB has a structural architecture.

© Sabih H. Gerez, University of Twente, The Netherlands

SYSTEM-ON-CHIP DESIGN

GETTING STARTED WITH VHDL

21

## **REPORT GUIDELINES (1)**

- Upload report to Canvas.

- Report text in PDF.

- VHDL source files converted to PDF (all files created by you including configurations; in principle, you do not modify any of the provided files).

- List of VHDL files in report.

- Be to the point: too much and too little text are penalized.

- Page limits are provided per project, per exercise.

- Do not copy the entire project text into your report.

- Do not report on results of *training* exercises.

- When answering questions, motivate where possible, especially motivate design choices.

#### **JI.** GETTING STARTED WITH VHDL

September 2, 2022

22

# **REPORT GUIDELINES (2)**

- Provide *block diagrams* to illustrate your design's structure.

- Include waveforms appropriate to what you want to show:

- Make a motivated selection of the signals in the design (just dumping all signals may be penalized).

- Choose an appropriate format: binary, decimal, hexadecimal ...

- Choose an appropriate time span.

- Make sure the waveforms are readable, also after printing on paper.

- Image: System-ON-CHIP DESIGN

23

Image: System-ON-CHIP DESIGN

23

GETTING STARTED WITH VHDL

September 2, 2022

Image: Next Steps

Go to the lab (ZI West).

Students already registered in Canvas should have access to the lain war access to the lain was access to the lain war access the lain war access to the lain war access the lain war access to the lain war access the lain war access to the lain was access to the lain war access to the lai

- the Linux server. Contact the assistant if you don't have access to Osiris/Canvas.

- Do not rush in doing the exercises. Take your time to study the handouts.

- For questions, try to contact the teaching assistant (with "Horusapp" on Thursday mornings, see slides on organization).