#### UNIVERSITY OF TWENTE.

September 6, 2022

#### SYSTEM-ON-CHIP DESIGN LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

3

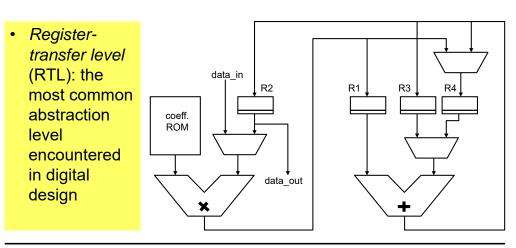

# **REGISTER-TRANSFER LEVEL (1)**

September 5, 2022

#### OUTLINE

- Register-transfer level design

- Edge-triggered flipflops

- Standard cells

- Delay

- Logic optimization

- Clock skew and clock trees

Note: some of the slide material for this presentation has been taken from the slides belonging to:

Wolf, W., *Modern VLSI Design, System-on-Chip Design*, Third Edition, Prentice Hall PTR, Upper Saddle River, New Jersey, (2002).

#### © Sabih H. Gerez, University of Twente, The Netherlands

LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

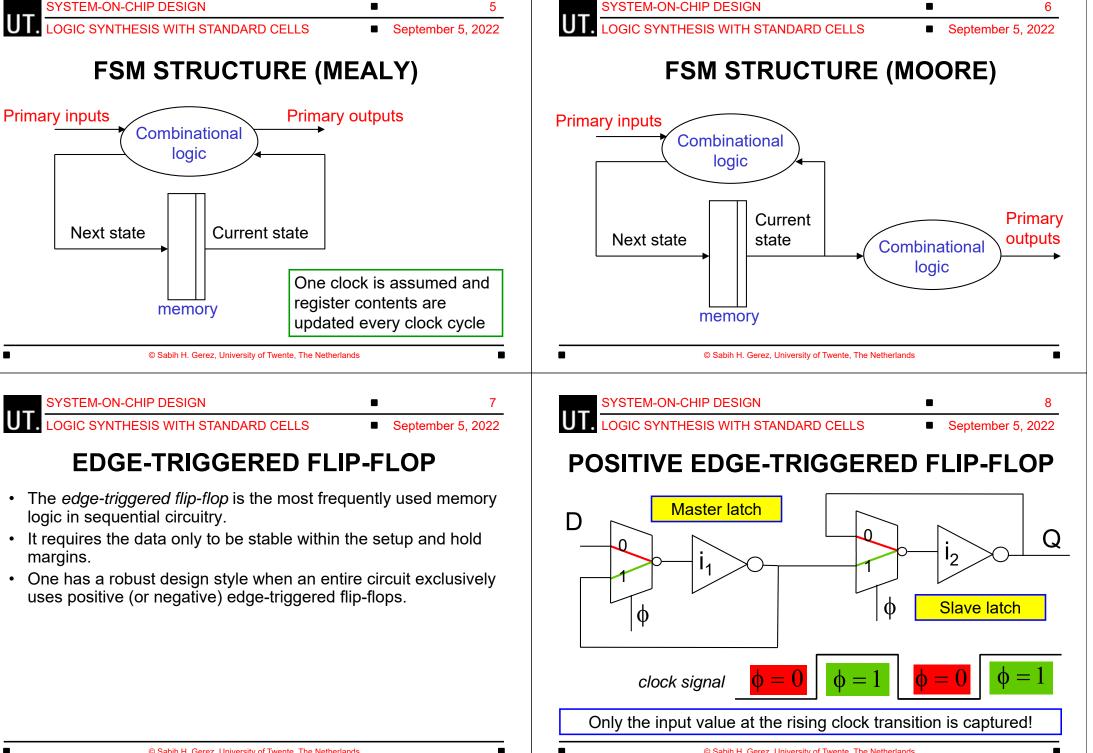

## **REGISTER-TRANSFER LEVEL (2)**

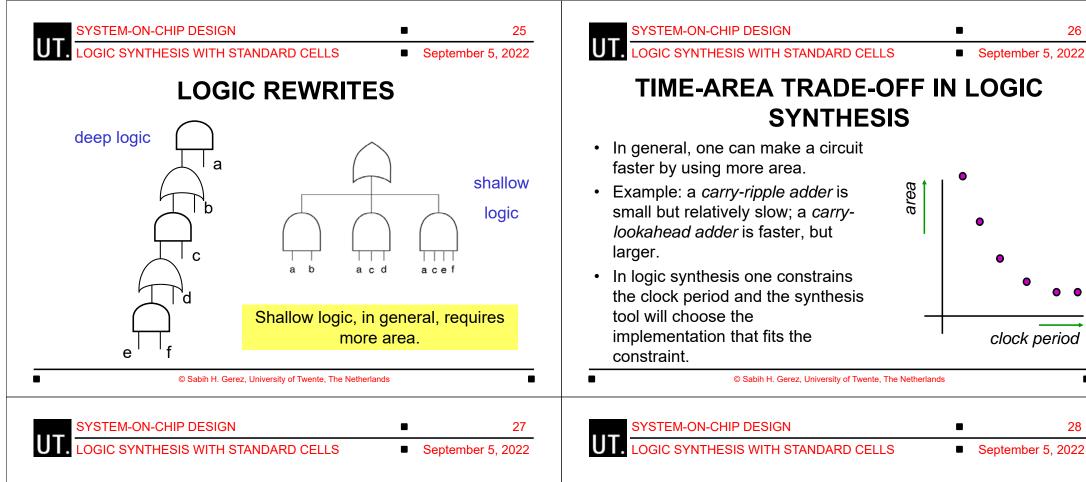

- Signals start either in a register or a *primary input*.

- Signals end either in a register or a primary output.

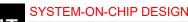

- Registers change their value at the rising edge of the clock (implemented by positive edge-triggered flipflops).

- Signals have time to propagate through *combinational logic* until next rising edge of clock.

- Hardware behaves as a *finite state machine* (FSM), where the registers hold the *current state* and the combinational logic computes the *next state*.

٠

<sup>©</sup> Sabih H. Gerez, University of Twente, The Netherlands

LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

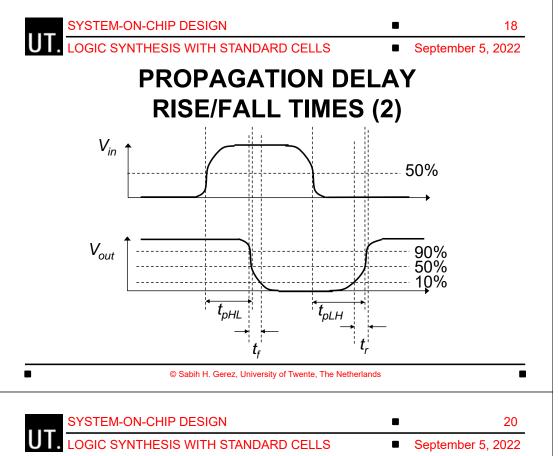

#### **MASTER-SLAVE OPERATION**

- Φ = 0: master latch output follows input D; slave latch keeps its value.

- Rising edge of Φ: value of D now propagates to slave's output.

- Φ = 1: master latch keeps its value; slave latch is transparent and follows master.

SYSTEM-ON-CHIP DESIGN

LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

10

#### **STANDARD-CELL-BASED DESIGN (1)**

- The designer is given a *library* of elementary circuits called *cells*.

- The design of library cells (from transistors) is a specialized task and is done by a dedicated group or company.

- Library information consists of:

- cell function and simulation models (delays!)

- cell layouts.

© Sabih H. Gerez, University of Twente, The Netherlands

UT. LOGIC SYNTHESIS WITH STANDARD CELLS

SYSTEM-ON-CHIP DESIGN

September 5, 2022

11

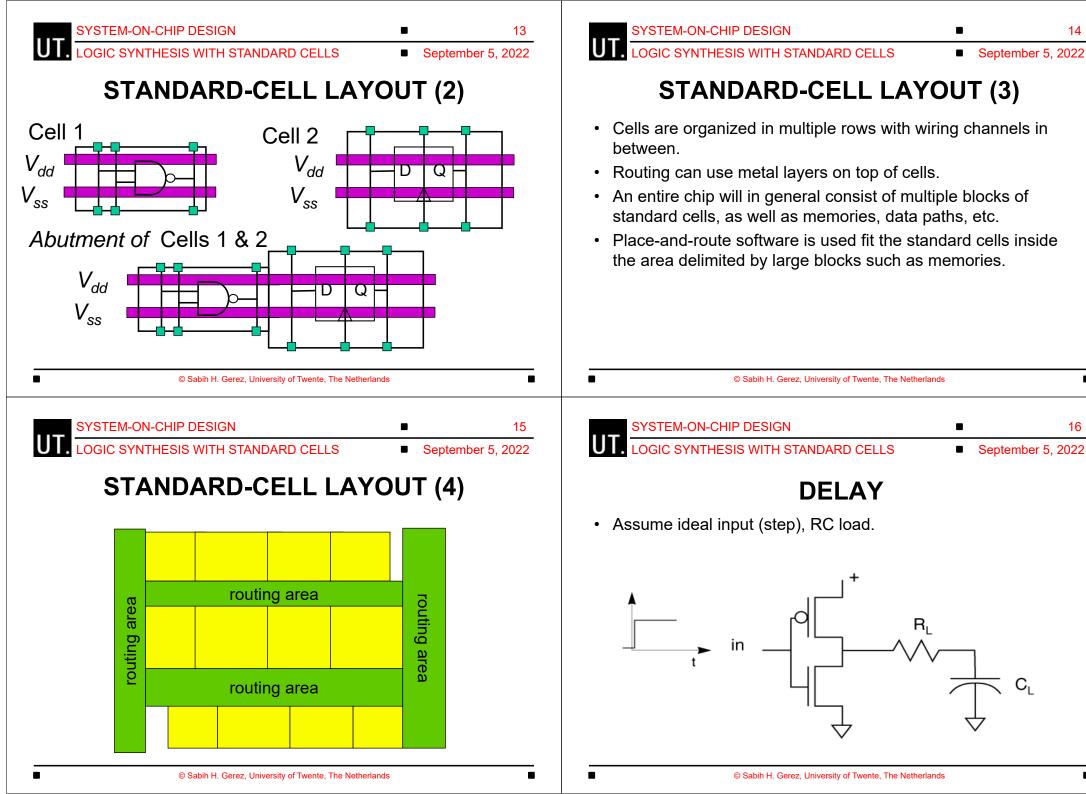

## **STANDARD-CELL-BASED DESIGN (2)**

- Designing amounts to delivering a *netlist* of cells for layout.

- The netlist is generally obtained by means of logic synthesis.

- The netlist is mapped on a layout by means of *placement* and *routing*.

SYSTEM-ON-CHIP DESIGN

LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

12

## **STANDARD-CELL LAYOUT (1)**

© Sabih H. Gerez, University of Twente, The Netherlands

- Cells use a limited number of metal layers.

- Power wires run horizontally through the cells using the same pitch; horizontal cell *abutment* can be applied.

- Other wires have *terminals* on the top and/or bottom of the cell; wiring channels realize the interconnection of terminals according to netlist.

LOGIC SYNTHESIS WITH STANDARD CELLS

17

September 5, 2022

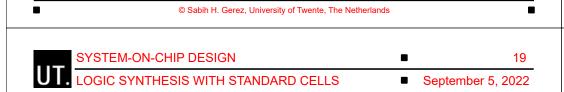

#### PROPAGATION DELAY RISE/FALL TIMES (1)

- *Propagation delay* is measured between the 50% transition moment of input and the 50% transition of output; it is the average of *high-to-low* and *low-to-high* delays.

- *Rise time* is measured from the 10% to the 90% points in the output transition.

- Fall time is the reverse (from 90% to 10%).

#### DRIVING LARGE LOADS

- Sometimes, large loads must be driven:

- off-chip;

- long wires on-chip.

- Sizing up the driver transistors only pushes back the problem driver now presents larger capacitance to earlier stage.

The standard-cell library has cells AND2D1, AND2D2, AND2D4:

What is the difference between the cells?

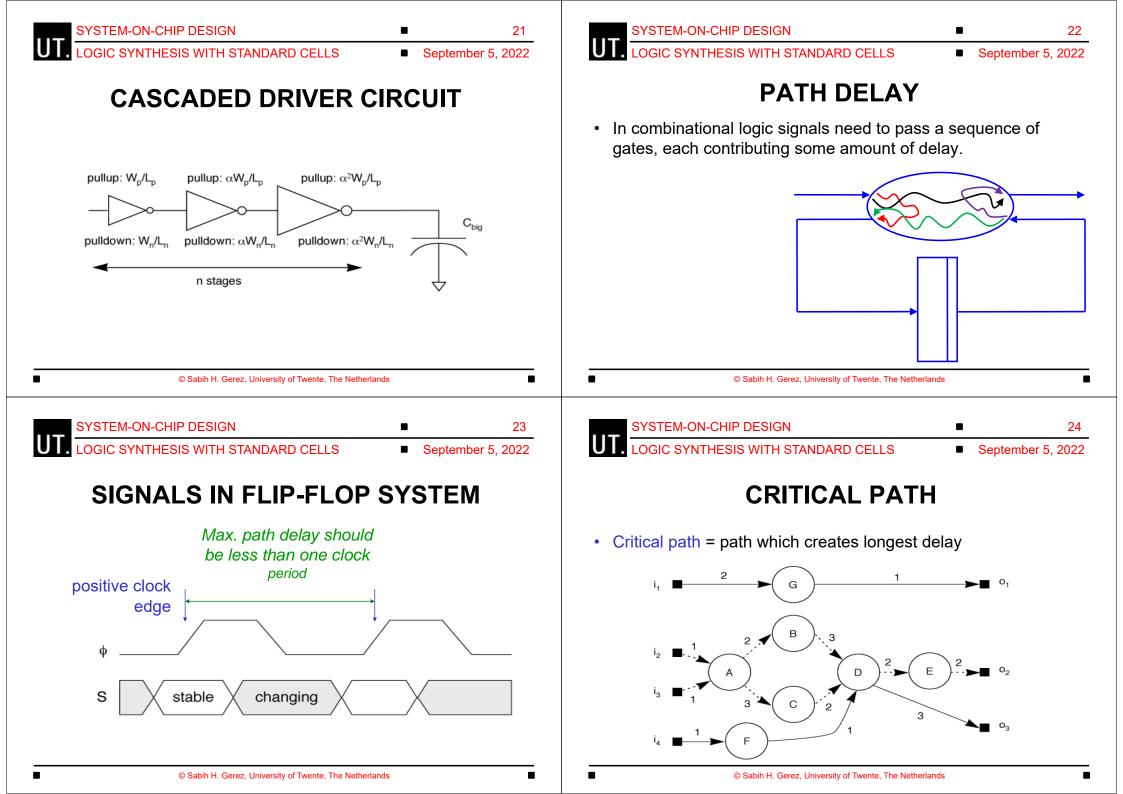

#### **OPTIMAL SIZING**

- Use a chain of inverters, each stage has transistors larger than previous stage.

- Optimal number of stages n<sub>opt</sub> = ln(C<sub>big</sub>/C<sub>g</sub>).

- Driver sizes are exponentially tapered.

#### **TECHNOLOGY-INDEPENDENT OPTIMIZATIONS**

- Works on Boolean expression equivalent.

- Estimates size based on number of literals.

- Uses factorization, resubstitution, minimization, etc. to optimize logic.

- Technology-independent phase uses simple delay models.

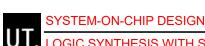

LOGIC OPTIMIZATION

Logic synthesis programs transform Boolean expressions into

Optimization goals: minimize area, meet delay constraint.

logic gate networks in a particular library.

26

28

LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

29

#### **TECHNOLOGY-DEPENDENT OPTIMIZATIONS**

- Maps Boolean expressions into a particular cell library.

- Mapping may take area and delay into account.

- May perform some optimizations in addition to simple mapping.

- Allows more accurate delay models.

SYSTEM-ON-CHIP DESIGN

- In state-of-the-art design, technology-dependent optimization • continues during layout (placement and routing):

- Think of buffering to compensate for parasitic delays.

LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

30

# **CLOCK TERMINOLOGY**

- *Clock edge:* rising or falling transition.

- Duty cycle: fraction of clock period for which clock is active (e.g., for active-low clock, fraction of time that clock is 0).

UT. LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

31

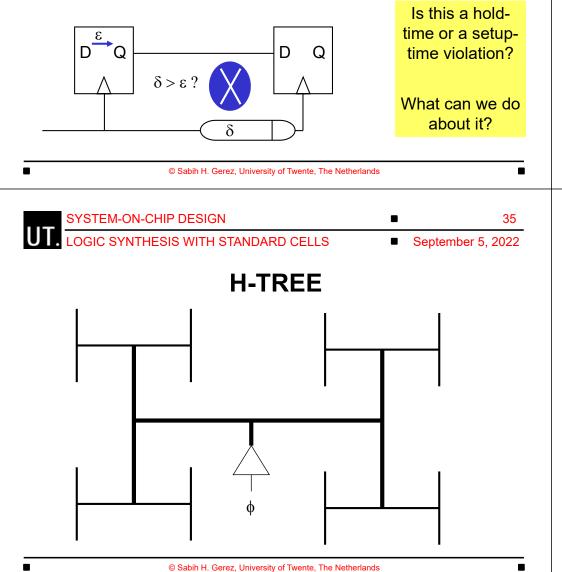

## **MEMORY-ELEMENT PARAMETERS**

© Sabih H. Gerez, University of Twente, The Netherlands

Setup time: time ٠ before clock edge etup time during which data σ input must be 0 stable. • Hold time: time after clock event clock for which data input must remain Stable Changing Changing data stable. © Sabih H. Gerez, University of Twente, The Netherlands

LOGIC SYNTHESIS WITH STANDARD CELLS

32 September 5, 2022

# **CLOCK SKEW (1)**

- · Clock must arrive at all memory elements in time to load data.

- The maximum difference between clock arrival times is the *clock skew*.

LOGIC SYNTHESIS WITH STANDARD CELLS

**CLOCK SKEW (2)**

Clock skew values larger than the flip-flop input-output delay lead to malfunctioning: some computations will be based on the next state rather than the current state.

UT. LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

34

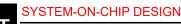

# **CLOCK DISTRIBUTION**

Goals:

33

September 5, 2022

- deliver clock to all memory elements with acceptable skew;

- deliver clock edges with acceptable sharpness.

- Clocking network design is one of the greatest challenges in the ٠ design of a large chip.

LOGIC SYNTHESIS WITH STANDARD CELLS

September 5, 2022

36

# **CLOCK TREE**

clk

FF2

FF3

© Sabih H. Gerez, University of Twente, The Netherlands

- In order to balance the delay from ٠ the clock source to the flip-flops, clock trees are used.

- They use optimal buffer sizing principles.

- In current-day practice clock trees ٠ are generated during layout as wiring delay is significant.

FF4