March 25, 2022

UT. SOFTWARE SYNTHESIS

March 25, 2022

#### **SOFTWARE SYNTHESIS**

Generation of executable code from data-flow graphs: singleprocessor schedules

- · Used for:

- Production software

- Simulation software

Think of the multiple calls to the *run* method in Arx C++ simulations.

Based on following paper (all examples are taken from it):

Bhattacharyya, S.S., R. Leupers and P. Marwedel, *Software Synthesis* and *Code Generation for Signal Processing Systems*, IEEE Transactions on Circuits and Systems---II, Analog and Digital Signal Processing, Vol.47(9), (September 2000).

© Sabih H. Gerez, University of Twente, The Netherlands

SOFTWARE SYNTHESIS

Implementation of Digital Signal Processing

Sabih H. Gerez

University of Twente

© Sabih H. Gerez, University of Twente, The Netherlands

UT. IMPLEMENTATION OF DSP SOFTWARE SYNTHESIS

March 25, 2022

# TOPICS

- Synchronous data flow (recap)

- Optimization criteria

March 25, 2022

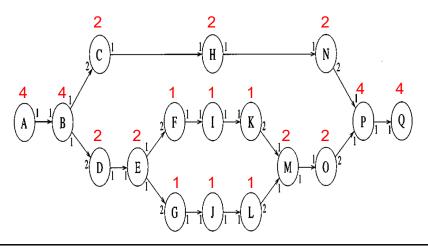

## SYNCHRONOUS DATA FLOW (SDF)

- · Already discussed.

- Each firing of a node consumes a fixed number of tokens and produces a fixed number of tokens (these numbers are annotated along the edges).

- An edge can have delay (initial tokens).

- Consistency:

- The repetitions vector (relative number of invocations for each node) should exist.

- There should be no *deadlock* (situation where nodes are waiting for each other to produce tokens).

March 25, 2022

UT. SOFTWARE SYNTHESIS

March 25, 2022

### **CONSISTENT SDF EXAMPLE**

© Sabih H. Gerez, University of Twente, The Netherlands

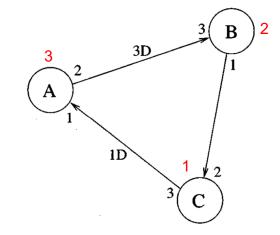

### **EXAMPLE OF SDF WITH DEADLOCK**

Easiest check for deadlock: simulation

IMPLEMENTATION OF DSP

nD on an edge means, n initial tokens.

4D on edge AB removes deadlock.

© Sabih H. Gerez, University of Twente, The Netherlands

### **OPTIMIZATION CRITERIA**

- · Buffer memory

- Code memory

- · Number of context switches

### **IMPLEMENTATION**

- Inlined code

- **Subroutines**

- Hybrid

March 25, 2022

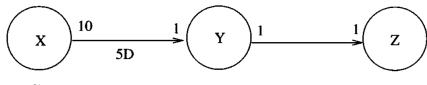

## MINIMAL-BUFFER SCHEDULE

$S_1 = YZYZYZYZYZYZYZYZYZYZYZ$

- Buffer size:  $\mathit{buf}(S_1) = 11$

- Code size:  $c_size(S_1) = \kappa(X) + 10\kappa(Y) + 10\kappa(Z)$

- Context switches:  $C_SW(S_1) = 21$

March 25, 2022

SOFTWARE SYNTHESIS

IMPLEMENTATION OF DSP

March 25, 2022

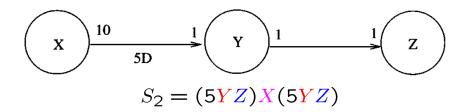

### LOOPED SCHEDULE

- Buffer size:  $buf(S_2) = 11$

- Code size:  $c_size(S_2) \approx \kappa(X) + 2\kappa(Y) + 2\kappa(Z)$

- Context switches:  $C_{-}SW(S_2) = 21$

© Sabih H. Gerez, University of Twente, The Netherlands

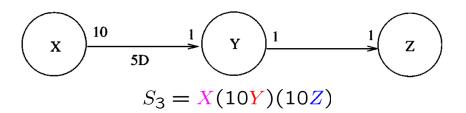

# MINIMAL-CODE-SIZE SCHEDULE (1)

- Buffer size:  $buf(S_3) = 25$

- Code size:  $c\_size(S_3) \approx \kappa(X) + \kappa(Y) + \kappa(Z)$

- Context switches:  $C_{-}SW(S_3) = 3$

© Sabih H. Gerez, University of Twente, The Netherlands

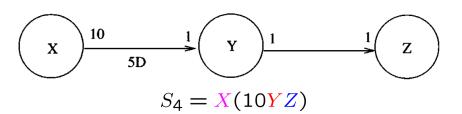

## **MINIMAL-CODE-SIZE SCHEDULE (2)**

- Buffer size:  $buf(S_4) = 16$

- Code size:  $C_Size(S_4) \approx \kappa(X) + \kappa(Y) + \kappa(Z)$

- Context switches:  $C_SW(S_4) = 21$